先进封装解决方案

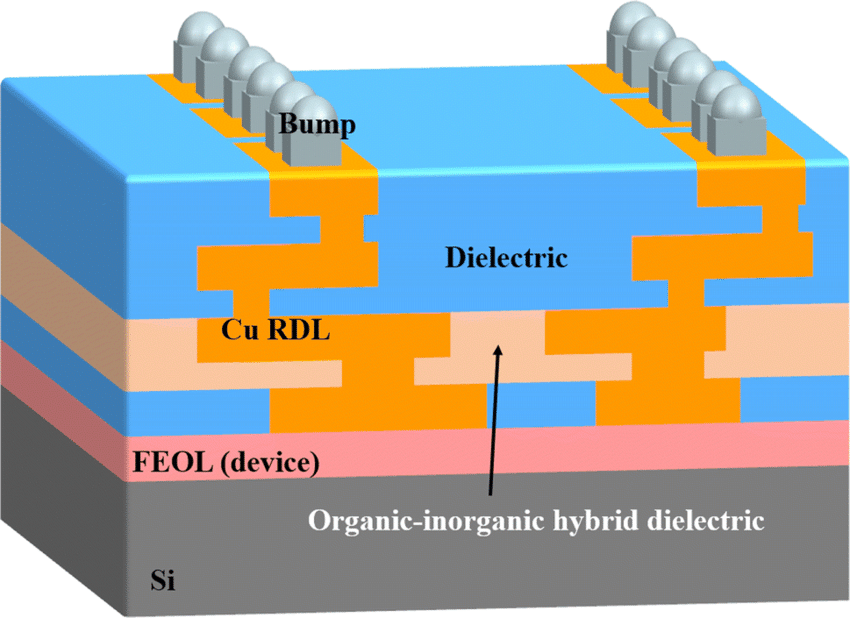

晶圆级先进封装FOWLP

是一种创新的半导体封装技术。其核心在于将传统后道封装工艺(如贴装、互连、成型)直接转移到整片晶圆上进行,而不是对单个切割好的芯片(Die)逐个处理。FOWLP 最显著的特点是“扇出”(Fan-Out),它允许芯片的输入/输出(I/O)触点通过重新布线层(RDL)扩展到芯片自身的物理尺寸之外。

这种技术省去了传统封装中的基板和引线键合,显著减小了封装尺寸和厚度,提升了电性能和散热效率,同时降低了成本。

FOWLP 尤其适用于对尺寸、性能和集成度要求极高的应用,如智能手机、物联网设备、高性能计算和人工智能芯片,是推动半导体持续微型化和高性能化发展的关键技术之一。

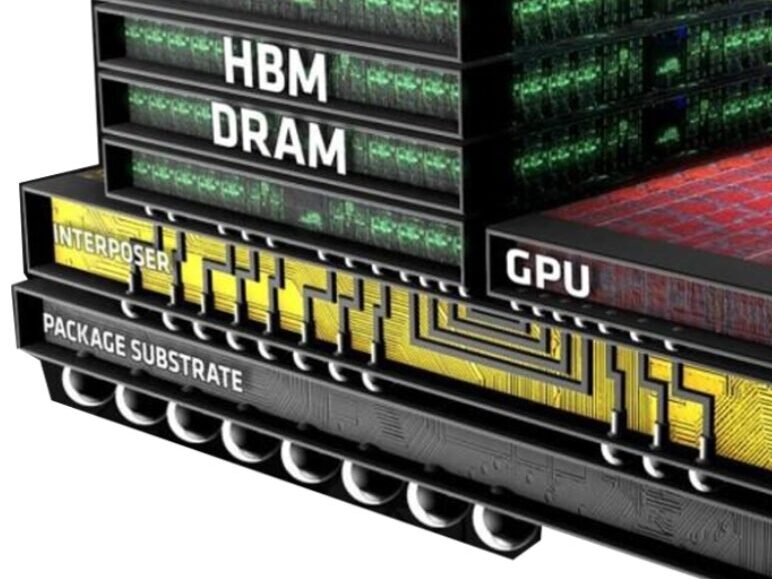

COWOS/HBM

CoWoS (Chip on Wafer on Substrate) 是一种由台积电(TSMC)开发的2.5D/3D先进封装技术。它的核心在于使用一块硅中介层 (Silicon Interposer) 作为载体。先将多个芯片(如高性能计算芯片、HBM内存等)以极高密度和带宽“Chip-on-Wafer” (CoW) 的方式集成到中介层晶圆上;然后,再将这个包含芯片的中介层晶圆整体“Wafer-on-Substrate” (WoS) 封装到一个传统的有机基板上。CoWoS通过中介层内精密的硅通孔 (TSV) 和超高密度布线,实现了芯片间超短距离、超高带宽和低功耗的互连,是高性能计算(HPC)、人工智能(AI)加速器和高端GPU的关键使能技术。

HBM (High Bandwidth Memory) 则是一种革命性的高带宽内存技术标准。它通过将多个DRAM裸片(Die)像楼层一样垂直堆叠起来(3D堆叠),并通过硅通孔 (TSV) 和微凸块进行互连,最后与一个逻辑控制芯片(Base Die)封装在一起,形成一个紧凑的立方体。HBM的核心优势在于其极其宽阔的内存总线(通常1024bit起,远高于传统GDDR的32/64bit) ,这使得它能在相对较低的时钟频率下提供远超传统内存的惊人带宽(可达数百GB/s甚至超过1TB/s)。

两者的结合: CoWoS封装平台是实现HBM与处理器(如CPU、GPU、AI芯片)高性能、高密度集成的首选方案。将HBM堆栈通过CoWoS的中介层与计算芯片紧邻放置并互连,能最大化发挥HBM的超高带宽潜力,满足最苛刻的计算需求。因此,“CoWoS + HBM” 已成为顶级AI加速卡和超级计算机芯片的黄金组合。

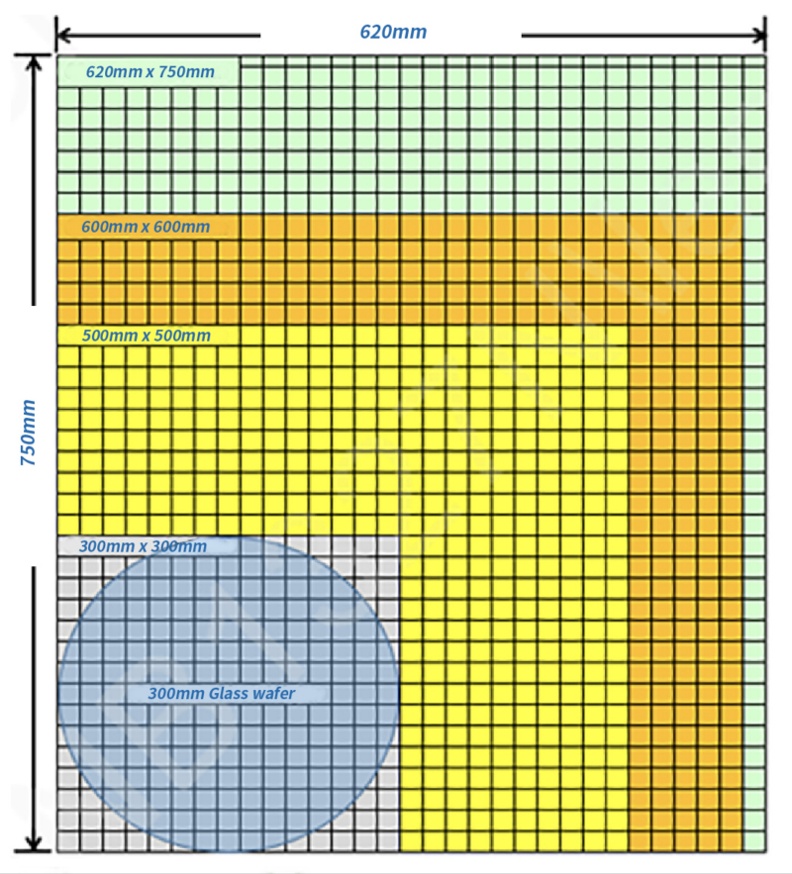

板级先进封装FOPLP

板级先进封装(FOPLP, Fan-Out Panel Level Packaging) 是扇出型封装技术的重要延伸与创新。其核心理念借鉴了晶圆级扇出封装(FOWLP),但将加工载体从圆形硅晶圆升级为更大的矩形面板(Panel)(通常面积大于500mm²,远大于300mm晶圆)。FOPLP直接在面板上对多个芯片进行高密度布局、模塑料(EMC)封装成型、构建高精细度的重新布线层(RDL)以实现“扇出”互连,最后切割成单个封装体。FOPLP的核心优势在于利用更大的面板尺寸实现更高的生产效率和显著的成本降低潜力,尤其适合需要大规模量产的消费电子、物联网、汽车电子等中高端芯片封装。它被视为突破传统晶圆尺寸限制、推动扇出封装进一步降本普及的关键技术方向,但也面临着面板均匀性控制、高精度对位等制造挑战。

深圳市伊乐电子有限公司

深圳市龙岗区宝龙街道同心社区长湖围工业区9号S7栋101

华南地区联系方式:Yvette 13410131178

华东地区联系方式:Robert 13424322768