COWOS/HBM

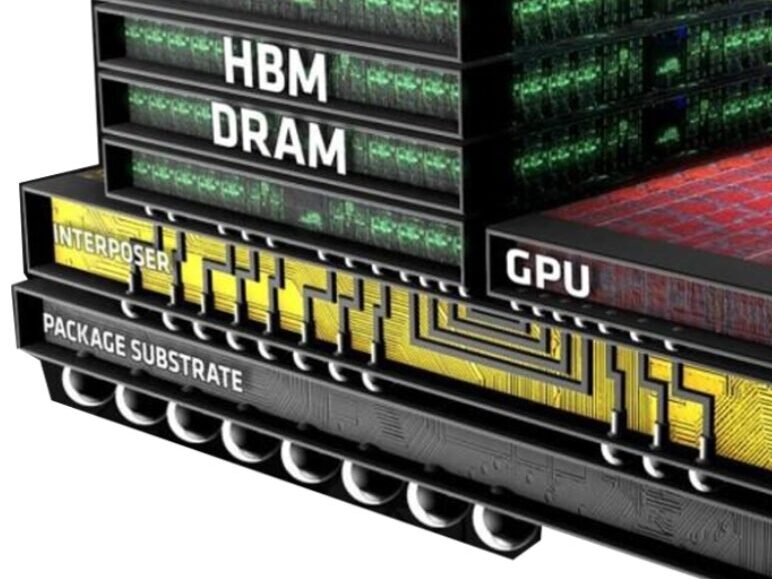

CoWoS (Chip on Wafer on Substrate) 是一种由台积电(TSMC)开发的2.5D/3D先进封装技术。它的核心在于使用一块硅中介层 (Silicon Interposer) 作为载体。先将多个芯片(如高性能计算芯片、HBM内存等)以极高密度和带宽“Chip-on-Wafer” (CoW) 的方式集成到中介层晶圆上;然后,再将这个包含芯片的中介层晶圆整体“Wafer-on-Substrate” (WoS) 封装到一个传统的有机基板上。CoWoS通过中介层内精密的硅通孔 (TSV) 和超高密度布线,实现了芯片间超短距离、超高带宽和低功耗的互连,是高性能计算(HPC)、人工智能(AI)加速器和高端GPU的关键使能技术。

HBM (High Bandwidth Memory) 则是一种革命性的高带宽内存技术标准。它通过将多个DRAM裸片(Die)像楼层一样垂直堆叠起来(3D堆叠),并通过硅通孔 (TSV) 和微凸块进行互连,最后与一个逻辑控制芯片(Base Die)封装在一起,形成一个紧凑的立方体。HBM的核心优势在于其极其宽阔的内存总线(通常1024bit起,远高于传统GDDR的32/64bit) ,这使得它能在相对较低的时钟频率下提供远超传统内存的惊人带宽(可达数百GB/s甚至超过1TB/s)。

CoWoS封装平台是实现HBM与处理器(如CPU、GPU、AI芯片)高性能、高密度集成的首选方案。将HBM堆栈通过CoWoS的中介层与计算芯片紧邻放置并互连,能最大化发挥HBM的超高带宽潜力,满足最苛刻的计算需求。因此,“CoWoS + HBM” 已成为顶级AI加速卡和超级计算机芯片的黄金组合。

COWOS/HBM-主要工艺及设备方案

COWOS/HBM的主要流程包括:

- 硅中介层制备(关键载体)

- TSV 加工:在硅晶圆上刻蚀 硅通孔(Through-Silicon Via, TSV) → 填充铜(导电材料),实现垂直互连。

- 高密度布线:通过半导体工艺(光刻、镀铜、蚀刻)制作 微米级重布线层(RDL),形成超高密度互连网络。

- 微凸块(Microbumps)成型:在布线层表面制备微凸块(直径 10-25μm),作为芯片贴装的电性接口。

- Chip-on-Wafer(CoW)—— 芯片集成到中介层

- 高精度贴片:将 计算芯片(如 GPU/ASIC) 和 HBM 内存堆栈 通过 热压键合(Thermo-Compression Bonding) 精准对齐并键合到中介层的微凸块上。

- 底部填充(Underfill):注入环氧树脂填充芯片与中介层间隙,增强机械强度并改善散热。

- Wafer-on-Substrate(WoS)—— 基板封装

- 中介层切割:将完成芯片集成的中介层晶圆切割成单颗单元(每个单元含计算芯片 + HBM)。

- 基板键合:将单元倒装焊至 大型有机基板(通过焊球/BGA 连接),基板提供外部 PCB 接口。

- 塑封与植球:用环氧模塑料(EMC)封装保护结构,并在基板底部植入 焊球阵列。

- 测试与验证

- 执行 电性测试(信号完整性、功耗)、热测试(散热性能)、可靠性测试(温度循环、机械应力)及外观AOI筛选

伊乐电子提供的设备方案

深圳市伊乐电子有限公司

深圳市龙岗区宝龙街道同心社区长湖围工业区9号S7栋101

华南地区联系方式:Yvette 13410131178

华东地区联系方式:Robert 13424322768